# New Phase Current Balancing Control for a Cryogenic Ultra-Low-Loss Bidirectional Multi-Phase Full-Bridge DC-DC Step-Down Converter

M. Akbas, D. Zhang, J. W. Kolar, and J. Huber Power Electronic Systems Laboratory, ETH Zurich, Switzerland

Abstract—This paper proposes a new phase current balancing control method for multi-phase full-bridge step-down dc-dc converters with bipolar output voltage, targeting cryogenic ultra-lowloss power supplies for high-temperature-superconducting (HTS) magnet systems of future particle accelerators. Achieving ultralow losses requires balanced average phase currents but prohibits the use of dedicated phase current sensors or shunts. Therefore, the proposed method reconstructs the phase current imbalance information by indirectly sensing the dc input capacitor current via the dv/dt and processing it in the frequency domain with low computational complexity. Compared to similar existing methods that only target half-bridge dc-dc step-down converters, the proposed method supports full-bridge topologies and high phase counts, as confirmed by detailed circuit simulations with 12 fullbridge phase modules. Finally, the balancing can be improved by phase inductance estimates based on indirectly sensing the output capacitor current, and carrier-to-phase reassignment utilizing the balancing controller information ensures optimum ripple cancellation at the output.

*Index Terms*—Cryogenic power electronics, multi-phase converters, phase current balancing, full-bridge converters.

#### I. INTRODUCTION

To enable new discoveries in physics, the feasibility of a new large-scale particle accelerator, the future circular collider (FCC), with a circumference of 80-100 km, about three times that of the Large Hadron Collider (LHC) at CERN in Geneva, Switzerland, is currently being studied [1]. Particle accelerators require various types of very strong electromagnets for guiding the particle beams. Aiming at minimizing the FCC's energy consumption, state-of-the-art room-temperature normal-conducting magnets (with high conduction losses) or low-temperature-superconducting magnets (with high power requirement of the cooling systems) should be replaced by high-temperature-superconducting (HTS) magnet systems. Still, the

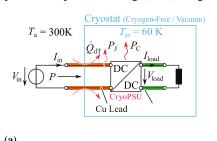

thick current leads connecting an HTS magnet, which resides in a cryostat, with the outside power supply unit (PSU), lead to a significant heat leak-in and a corresponding power demand of the cryocoolers. If instead a dc-dc step-down converter is placed inside of the magnet's cryostat, i.e., operates at around  $70\,\mathrm{K}$  as indicated in **Fig. 1a**, the current leads can be designed for a much lower current and hence the leak-in losses are reduced. On the other hand, targeting a reduction of the cryocooler heat load by a factor of 4 compared to the state of the art with thick current leads, the loss budget for the cryogenic dc-dc step-down converter is very tight (specifically,  $< 5\,\mathrm{W}$  for a magnet current of 250 A) [2].

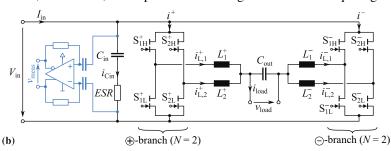

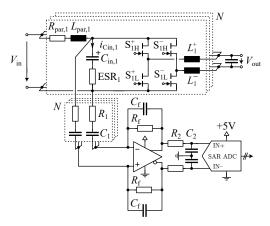

To enable low conduction losses and four-quadrant operation, a full-bridge multi-phase step-down converter topology as shown in **Fig. 1b** is selected [2]. Ensuring minimum losses further requires an equal load current sharing among the converter phases. However, phase-to-phase mismatches of up to  $\pm 10\%$  for the phase inductances and up to  $\pm 50\%$  for the transistors' on-state resistances must be expected, which cause phase current imbalances in practical multi-phase converter realizations, and thus closed-loop control of the (average) phase-currents is needed [3]–[9].

Literature discusses various implementation options, mainly targeting half-bridge-type dc-dc step-down converters without bipolar output voltage capability, e.g., for CPU voltage regulator modules. Typically, each phase current is measured using dedicated current sensors, dedicated shunt resistors or via the low-frequency (resistive) voltage drop across the phase inductors [3]; however, the tight loss budget of the considered application requires that any series resistances are minimized. Thus, also passive balancing mechanisms requiring zero-

Fig. 1. (a) Concept of a cryogenic power supply for high-temperature-superconducting (HTS) magnets, where an ultra-low-loss dc-dc step-down converter operates inside of the magnet's cryostat at 70 K. (b) Considered full-bridge multi-phase dc-dc step-down converter topology with a simplified representation of the indirect input capacitor current sensing circuit (based on measuring the capacitor voltage  $\mathrm{d}v/\mathrm{d}t$ ) needed for the proposed phase current balancing method. Note that only N=2 phases per branch are shown to facilitate the explanations (see Fig. 2 for key waveforms); practical realizations feature more phases depending on the loss budget and the rated magnet current.

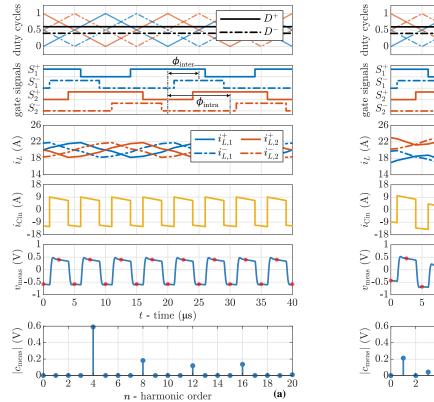

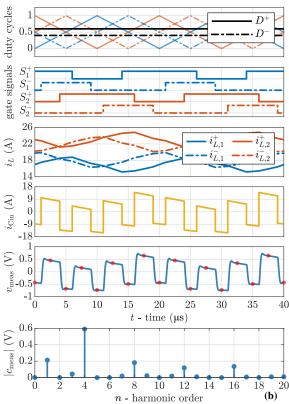

Fig. 2. Key waveforms of the full-bridge multi-phase dc-dc step-down converter from Fig. 1b with N=2 phases, a switching frequency of  $f_{\rm sw}=50\,{\rm kHz}$ , an input voltage of  $V_{\rm in}=1\,{\rm V}$ , and a dc load current of  $I_{\rm load}=40\,{\rm A}$ ; further,  $D^+=D_{\rm CM}+D_{\rm DM}$  and  $D^-=D_{\rm CM}-D_{\rm DM}$  are the duty cycles of the  $\bigoplus$  and  $\bigoplus$ -branch (see Fig. 1b), where  $D_{\rm CM}=0.5$  is the CM duty cycle and  $D_{\rm DM}$  is the DM duty cycle that defines the output voltage. (a) Fully symmetric conditions and hence equal current sharing (i.e., equal average values of all phase inductor currents  $i_{\rm L}$ ) and (b) considering component mismatches and hence unequal current sharing among the phases, which affects the dc input capacitor current  $i_{\rm Cin}$  and thus the time-domain waveform and the spectrum of the sensing circuit's output voltage  $v_{\rm meas}$  (note that the harmonic order n=1 corresponds to the device switching frequency  $f_{\rm sw}$ ). The sampling instants of  $v_{\rm meas}$  (with  $f_{\rm sample}=2\cdot 2Nf_{\rm sw}$ ) that are used by the proposed balancing controller from Fig. 4 are indicated by red dots (•).

voltage-switching (ZVS) designs [4], [5] with (approximately) 30% higher conduction losses are not applicable. Alternatively, the phase currents could be reconstructed using a single current sensor on the dc input side and the switching state information [7], [8]; these methods are, however, only feasible for low duty-cycles  $(D \leq \frac{1}{2N})$  or converters with a low phase count N due to the computational complexity of the involved matrix inversions

Finally, as indicated in **Fig. 2**, the dc input capacitor current (and/or voltage ripple) contains the phase current information. As proposed for a half-bridge multi-phase buck converter in [9], the indirectly (via the capacitor voltage  $\mathrm{d}v/\mathrm{d}t$ ) sensed input capacitor current can be processed in the frequency domain to extract the phase current imbalance information (if not the absolute values). However, the approach from [9] is limited to a half-bridge topology with unipolar output voltage only, to a narrow operating range (e.g., output voltage/current) or a fixed operating point, depends on the equivalent series resistance (ESR) of the input capacitor, and the robustness as well as the implementation with a large number of interleaved phases (e.g., N > 8) has not been demonstrated so far.

Therefore, this work proposes a new extended/improved phase current balancing method for full-bridge multi-phase dc-dc converters (see **Fig. 1b**) based on the processing of the indirectly sensed input dc capacitor current in the frequency

domain. The method supports a wide operating range, a high phase count (e.g., N>8) and shows low dependency on the input dc capacitor's equivalent series resistance (ESR). In the following, **Section II** first discusses the optimum modulation scheme of full-bridge multi-phase converters before **Section III** introduces the proposed phase current balancing method. **Section IV** discusses the implementation and improvement vectors, and **Section V** concludes the paper.

#### II. CONVERTER OPERATION

The key converter waveforms are illustrated in Fig. 2 for the case of N=2 phases each in the  $\bigoplus$ -branch and in the  $\bigoplus$ -branch as shown in Fig. 1. The thus N individual carriers per branch are interleaved using the intra-branch interleaving angles of  $\phi_{\text{intra}}=2\pi/N\cdot(x-1)$  for  $x\in[1,N]$ . Furthermore, the carriers of the  $\bigoplus$ - and  $\bigoplus$ -branch are phase shifted by the interbranch interleaving angle  $\phi_{\text{inter}}$  against each other. The branch duty cycles  $D^+$  and  $D^-$  follow from the desired common-mode (CM) and differential-mode (DM) voltage components at the output of the multi-phase full-bridge converter, i.e.,

$$D_{\rm CM} = \frac{D^+ + D^-}{2}$$

and  $D_{\rm DM} = \frac{D^+ - D^-}{2}$ . (1)

The DM duty-cycle  $D_{\rm DM}$  is used to control the output voltage  $v_{\rm load}$ , whereas the CM duty cycle  $D_{\rm CM}$  and also the inter-phase interleaving angle  $\phi_{\rm inter}$  are degrees of freedom (DoF) that can

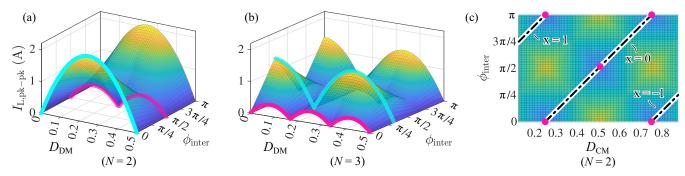

Fig. 3. Exemplary output current switching ripple cancellation depending on  $D_{\rm DM}$  and the inter-branch interleaving angle  $\phi_{\rm inter}$  for a CM duty cycle of  $D_{\rm CM}=0.5$  and an (a) even number of N=2 and (b) odd number of N=3 phases; selecting the optimum  $\phi_{\rm inter}$  results in minimum output current ripple (•) compared to a suboptimal choice (•). (c) Optimum choice (resulting in minimum output current ripple) of the inter-branch interleaving angle  $\phi_{\rm inter}$  in dependence of the CM duty cycle  $D_{\rm CM}$  for N=2 and  $D_{\rm DM}=0.125$ .

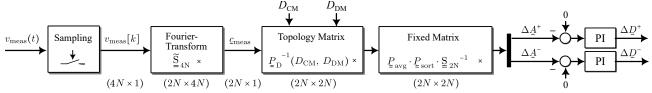

Fig. 4. Proposed closed-loop phase-current balancing controller for full-bridge multi-phase dc-dc converters as shown in Fig. 1b. The output signal of the indirect input capacitor current sensing circuit  $v_{\text{meas}}(t)$  is sampled (see Fig. 2) and processed in the frequency domain to obtain the phase current deviations  $\Delta \underline{A}^+$  and  $\Delta \underline{A}^-$  from the branch average, which are then controlled to zero by adapting the duty cycles of the individual half-bridges accordingly.

be adjusted for optimum ripple cancellation, see Fig. 3ab.  $D_{\rm CM}$  is typically selected to maximize the available dynamic range for  $D_{\rm DM}$  and the angle  $\phi_{\rm inter}$  is chosen to achieve an effective switching frequency (at the input and output) of  $f_{\rm eff}=2Nf_{\rm sw}$  and, thus, minimum required filtering effort. The optimum choices of the inter-branch interleaving angle  $\phi_{\rm inter}$  for a given  $D_{\rm CM}$  for odd and even number of phases N are

$$\phi_{\rm inter, opt.}\Big|_{\rm odd\ N} = \frac{2\pi}{N} \cdot x + (D_{\rm CM} - \frac{1}{2}) \cdot 2\pi \quad \text{and}$$

$$\phi_{\rm inter, opt.}\Big|_{\rm even\ N} = \frac{2\pi}{2 \cdot N} \cdot (2x+1) + (D_{\rm CM} - \frac{1}{2}) \cdot 2\pi, \quad (2)$$

where  $x\in\mathbb{Z}$ , which is illustrated in **Fig. 3c**. To obtain  $f_{\mathrm{eff}}=2Nf_{\mathrm{sw}}$  at both the input and output, the CM duty-cycle in (2) should be chosen as  $D_{\mathrm{CM}}=\frac{x}{2N}$  with  $x\in[1,2N-1]$ , which is marked by the pink dots  $\bullet$  in **Fig. 3c**.

Then, with respect to Fig. 2, the comparison of the dutycycles  $D^+$  and  $D^-$  for the (+)- and (-)-branches with the respective carrier signals results in the gate signals for the corresponding half-bridges. The phase inductor currents are balanced in the ideal case from Fig. 2a and the inductor current ripple cancels at both the input and the output as a result of the interleaved modulation. This ripple cancellation can also be observed in the input dc-link capacitor current waveform, which is indirectly sensed by measuring the input capacitor voltage dv/dt with an active high-pass circuit as depicted in Fig. 1, i.e., the sensing circuit output voltage  $v_{\rm meas}$ is proportional (adjustable via the gains of the measurement chain) to the (HF) dc-link capacitor current. Therefore, the ripple cancellation is visible in the harmonic spectrum  $v_{\text{meas}}$ , too. Fig. 2b depicts the same key waveforms for the case of unbalanced phase inductor currents, which result, e.g., from component mismatches like unequal on-state resistances amongst the transistors, etc. The unbalanced inductor currents

imply non-ideal ripple cancellation at the input and output of the converter as can be seen in the input capacitor current waveform and the harmonic spectrum of  $v_{\rm meas}$ ; specifically, components between the device switching frequency  $f_{\rm sw}$  and the effective switching frequency  $f_{\rm eff}=2Nf_{\rm sw}$  appear. The proposed phase current balancing controller uses these harmonics below  $f_{\rm eff}$  in  $v_{\rm meas}$  to determine the phase current unbalance, as explained in the following.

## III. PHASE CURRENT BALANCING METHOD

The core idea of the proposed method consists of equating analytical expressions (containing the phase current levels, the phase-specific carrier phase shifts, etc.) of the harmonic components (at the device switching frequency  $f_{\rm sw}$  and higher) of the input capacitor current with the digitally computed harmonic spectrum of the sensed input capacitor current to calculate the phase current imbalance information, i.e., the deviations from the average phase current in each branch,  $\Delta \underline{A}^+$  and  $\Delta \underline{A}^-$  (the underline denotes a vector); this is similar to [9], where, however, only half-bridge topologies are considered.

**Fig. 4** shows the block diagram of the closed-loop phase current balancing control implementation. Sensing the input capacitor voltage waveform with a properly designed analog signal conditioning circuit (see **Fig. 1b** and **Section IV-B**) yields a voltage signal  $v_{\rm meas}$  whose harmonic spectrum is equivalent to that of the input capacitor current in the frequency range of interest. Thus,  $v_{\rm meas}$  is sampled with a minimum sampling frequency of  $f_{\rm sample} = 2 \cdot 2N f_{\rm sw}$  to enable a reconstruction of 2N harmonic components below  $f_{\rm eff}$ . The sample vector  $v_{\rm meas}[k]$  is digitally processed with a truncated 4N-point discrete Fourier transform (DFT)  $\widetilde{\underline{S}}_{4N}$  to extract the complex spectrum  $\underline{c}_{\rm meas}$  (i.e., amplitude and phase of the harmonics) containing 2N harmonics.

The key challenge lies then in solving the resulting system of equations for the phase current imbalance information  $\Delta \underline{A}^+$  and  $\Delta \underline{A}^-$ , which requires a suitable modification of the equations to obtain a simple formulation and low computational effort for a microcontroller implementation, which is discussed in detail in **Section III-A**. Finally, low-bandwidth PI controllers are used to equalize the phase currents in each branch by applying minor modifications to the duty cycles of the individual bridge-legs.

# A. Phase Current Unbalance Estimation

The input capacitor current  $i_{\rm Cin}=I_{\rm in}-(i^++i^-)$  is composed of a dc component supplied from the input terminal (assuming sufficient impedance towards the feeding source, see **Section IV-A**) and of two pulsed current contributions from the multi-phase buck  $\bigoplus$ - and  $\bigoplus$ -branches. The pulsed currents  $i^+$  and  $i^-$  are comprised of the respective phase inductor currents  $i^+_{\rm L,1}, i^+_{\rm L,2}, \ldots, i^+_{\rm L,N}$  and  $i^-_{\rm L,1}, i^-_{\rm L,2}, \ldots, i^-_{\rm L,N}$  according to

$$i^{+} = \sum_{i=1}^{N} s_{i}^{+} \cdot i_{L,i}^{+}$$

and  $i^{-} = \sum_{i=1}^{N} s_{i}^{-} \cdot i_{L,i}^{-}$ , (4)

where  $s_{i}^{+}$  and  $s_{i}^{-}$  denote the switching state of the i-th bridgeleg of the  $\bigoplus$ - and  $\bigoplus$ -branch respectively. Following the general idea of [9], the complex-valued Fourier coefficients of the input capacitor current are

$$(c_{iCin})_{k} = (c_{I_{DC}})_{k}$$

$$-\underbrace{\frac{\sin(k \cdot \pi \cdot D_{+})}{k \cdot \pi}}_{\underline{K}^{+}} \cdot \sum_{m=0}^{N-1} \left( \underbrace{e^{-j \cdot \frac{2\pi \cdot k \cdot m}{N}}}_{\underline{N}} \cdot \underbrace{(A^{+})_{m}}_{\underline{A}^{+}} \right)$$

$$+ \underbrace{e^{-j \cdot k \cdot \phi_{inter}}}_{\underline{K}^{\phi}} \cdot \underbrace{\frac{\sin(k \cdot \pi \cdot D_{-})}{k \cdot \pi}}_{\underline{K}^{-}} \cdot \sum_{m=0}^{N-1} \left( \underbrace{e^{-j \cdot \frac{2\pi \cdot k \cdot m}{N}}}_{\underline{N}} \cdot \underbrace{(A^{-})_{m}}_{\underline{A}^{-}} \right),$$

$$(5)$$

where  $k \in \mathbb{N}_0$ ,  $\underline{c}_{\mathrm{I}_{\mathrm{DC}}}$  denotes the dc component resulting from the input side dc current  $I_{\mathrm{in}}$ ,  $(A^+)_{\mathrm{m}}$  and  $(A^-)_{\mathrm{m}}$  represent the average inductor currents of the (m+1)-th phase for the  $\oplus$ - and  $\ominus$ -branch respectively. As indicated below the braces in (5), the sum of the pulsed current contributions from the branches can be rewritten in matrix-vector notation by using the diagonal matrices  $\underline{K}^+$ ,  $\underline{K}^-$  and  $\underline{K}^\phi$ , and the N-point DFT matrix  $\underline{S}_{\mathrm{N}}$ . Note that  $\underline{c}_{\mathrm{I}_{\mathrm{DC}}} = [c_{\mathrm{I}_{\mathrm{DC}},0},0,\ldots,0]^T$  contains only a dc component, which cancels out in the final result (11) when carried through, and for simplicity will be

disregarded already from this point on. The same applies to the ac ripple components of the phase currents as long as equal phase inductances are considered (see also **Section IV-C**).

The obtained matrix-vector equation (5) contains 2N unknown average phase current values in total (N unknown currents  $\underline{A}^+$  and  $\underline{A}^-$  for the two branches, respectively), which appear, however, in pairs (as sums). Therefore, (5) provides only N equations (i.e., only N Fourier coefficients are considered) to solve for these 2N unknowns. In principle, however, more than N harmonics could be considered to increase the number of equations as needed. This can be elegantly implemented by combining the unknown ( $N \times 1$ ) vectors  $\underline{A}^+$  and  $\underline{A}^-$  conveniently by stagger-arranging the phase currents into a composite vector  $\underline{A} = [A_1^+, A_1^-, A_2^+, A_2^-, \dots]^T$ , introducing the masking matrices  $\underline{A}^+$  and  $\underline{A}^-$ , and extending the N-point DFT matrix  $\underline{S}_N$  to a 2N-point DFT matrix  $\underline{S}_N$ :

$$\underline{c}_{iCin} = -\underline{K}^{+} \cdot \underbrace{\underline{S}_{N} \cdot \underline{A}^{+}}_{= \underline{S}_{2N} \cdot \underline{M}^{+} \cdot \underline{A}}_{= \underline{S}_{2N} \cdot \underline{A}^{-}} + \underline{K}^{\phi} \cdot \underline{K}^{-} \cdot \underbrace{\underline{S}_{N} \cdot \underline{A}^{-}}_{= \underline{S}_{2N} \cdot \underline{M}^{-} \cdot \underline{A}}_{= \underline{S}_{2N} \cdot \underline{A}^{-} \cdot \underline{A}^{-}}_{= \underline{T}^{+} \cdot \underline{S}_{2N} \cdot \underline{A}} = \underline{T}^{-} \cdot \underline{S}_{2N} \cdot \underline{A}$$

$$= -\underline{K}^{+} \cdot \underline{T}^{+} \cdot \underline{S}_{2N} \cdot \underline{A} + \underline{K}^{\phi} \cdot \underline{K}^{-} \cdot \underline{T}^{-} \cdot \underline{S}_{2N} \cdot \underline{A}$$

$$= (-\underline{K}^{+} \cdot \underline{T}^{+} + \underline{K}^{\phi} \cdot \underline{K}^{-} \cdot \underline{T}^{-}) \cdot \underline{S}_{2N} \cdot \underline{A}$$

$$= \underline{P}_{D}$$

$$(6)$$

The final rearrangement advantageously features a conveniently invertible matrix on the right-hand side, i.e., the product of the unitary 2N-point DFT matrix  $\underline{\mathcal{G}}_{2N}$  and a  $(2\times 2)$  block-diagonal matrix  $\underline{\mathcal{P}}_{D}$ , which we will refer to as  $topology\ matrix$  in the following. The topology matrix  $\underline{\mathcal{P}}_{D}$  is given in (3) at the bottom of the page, and its entries are:

$$(k_{1}^{+})_{kk} = \frac{\sin(k \cdot \pi \cdot D^{+})}{k \cdot \pi} \qquad (k_{2}^{+})_{kk} = \frac{\sin((k+N) \cdot \pi \cdot D^{+})}{(k+N) \cdot \pi}$$

$$(k_{1}^{-})_{kk} = \frac{\sin(k \cdot \pi \cdot D^{-})}{k \cdot \pi} \qquad (k_{2}^{-})_{kk} = \frac{\sin((k+N) \cdot \pi \cdot D^{-})}{(k+N) \cdot \pi}$$

$$(k_{1}^{\phi})_{kk} = e^{-i \cdot k \cdot \phi_{\text{inter}}} \qquad (k_{2}^{\phi})_{kk} = e^{-i \cdot (k+N) \cdot \phi_{\text{inter}}}$$

$$(w)_{kk} = e^{i \cdot \frac{\pi}{N} \cdot k}. \qquad (7)$$

Solving for the phase current average information yields

$$\underline{A} = \underline{\underline{S}}_{2N}^{-1} \cdot \underline{\underline{P}}_{D}^{-1} \cdot \underline{\underline{c}}_{meas}

= \underline{\underline{S}}_{2N}^{-1} \cdot \underline{\underline{P}}_{D}^{-1} \cdot (\underline{\underline{\widetilde{S}}}_{4N} \cdot \underline{\underline{v}}_{meas}),$$

(8)

$^1{\rm These}$  are necessary to map the correct columns of  $\underline{S}_{2{\rm N}}$  with the corresponding entries/rows of  $\underline{A}.$

$$P_{\text{D}} = -\underbrace{\begin{pmatrix} K_{\pm 1}^{+} & 0 \\ 0 & K_{\pm 2}^{+} \end{pmatrix}}_{\underline{K}^{+}} \cdot \underbrace{\frac{1}{2} \begin{pmatrix} I_{\pm} & I_{\pm} \\ I_{\pm} & I_{\pm} \end{pmatrix}}_{\underline{I}^{\pm}} + \underbrace{\begin{pmatrix} K_{\pm 1}^{\phi} & 0 \\ 0 & K_{\pm 2}^{\phi} \end{pmatrix}}_{\underline{K}^{\phi}} \cdot \underbrace{\begin{pmatrix} K_{\pm 1}^{-} & 0 \\ 0 & K_{\pm 2}^{-} \end{pmatrix}}_{\underline{V}^{-}} \cdot \underbrace{\frac{1}{2} \begin{pmatrix} W_{\pm} & -W_{\pm} \\ W_{\pm} & -W_{\pm} \end{pmatrix}}_{\underline{I}^{-}} = -\frac{1}{2} \cdot \underbrace{\begin{pmatrix} K_{\pm 1}^{+} - K_{\pm 1}^{-} \cdot K_{\pm 1}^{\phi} \cdot W_{\pm} & K_{\pm 1}^{+} + K_{\pm 1}^{-} \cdot K_{\pm 1}^{\phi} \cdot W_{\pm} \\ K_{\pm 2}^{+} - K_{\pm 2}^{-} \cdot K_{\pm 2}^{\phi} \cdot W_{\pm} & K_{\pm 2}^{+} + K_{\pm 2}^{-} \cdot K_{\pm 2}^{\phi} \cdot W_{\pm} \end{pmatrix}}_{\underline{I}^{+}} = : -\frac{1}{2} \cdot \underbrace{\begin{pmatrix} X_{\pm}^{-} & U_{\pm} & U_{\pm} \\ V_{\pm} & V_{\pm} & V_{\pm} \end{pmatrix}}_{\underline{I}^{+}}$$

$$(3)$$

where  $c_{

m meas} = \widetilde{\underline{Z}}_{4

m N} \cdot \underline{v}_{

m meas}$  denotes the discrete complex spectrum of the sensing circuit output voltage.<sup>2</sup> Advantageously, the inverse of the  $(2 \times 2)$  block diagonal topology matrix  $P_{\rm D}$ can be evaluated analytically [10] as

$$P_{D}^{-1} = \frac{-2}{(X)_{kk}(Y)_{kk} - (U)_{kk}(V)_{kk}} \left(\frac{(Y)_{kk} - (U)_{kk}}{-(V)_{kk}(X)_{kk}}\right), (9)$$

with  $k \in [0, N-1]$  and where

$$(X)_{kk} = (k_1^+)_{kk} - (k_1^-)_{kk} \cdot (k_1^\phi)_{kk} \cdot (w)_{kk}$$

$$(U)_{kk} = (k_1^+)_{kk} + (k_1^-)_{kk} \cdot (k_1^\phi)_{kk} \cdot (w)_{kk}$$

$$(V)_{kk} = (k_2^+)_{kk} - (k_2^-)_{kk} \cdot (k_2^\phi)_{kk} \cdot (w)_{kk}$$

$$(Y)_{kk} = (k_2^+)_{kk} + (k_2^-)_{kk} \cdot (k_2^\phi)_{kk} \cdot (w)_{kk}.$$

$$(10)$$

Note that the k = 0 entry of each of the four diagonal matrices needs to be evaluated analytically by using L'Hôpital's rule. The numerical conditioning of the inverse topology matrix  $P_{\text{\tiny D}}^{-1}$ is further discussed in Section III-C. Finally, two auxiliary linear transformations,  $\underline{P}_{\mathrm{sort}}$  to sort the aggregate vector  $\underline{A}$  in order to obtain  $[\underline{A}^+,\underline{A}^-]^T$  and  $\underline{P}_{\mathrm{avg}}$  in order to have a relative measure for the phase current variations in each of the two branches, are used to finally obtain the relative deviations  $\Delta A$ of the individual phase currents from the branch-level mean

$$\Delta \underline{A} = \begin{bmatrix} \Delta \underline{A}^{+} \\ \Delta \underline{A}^{-} \end{bmatrix}$$

$$= \underbrace{\underline{P}_{\text{avg}} \cdot \underline{P}_{\text{sort}} \cdot \underline{S}_{\text{2N}}^{-1}}_{\text{Left}} \cdot \underline{P}_{\text{D}}^{-1} \cdot (\underline{\widetilde{S}}_{\text{4N}} \cdot \underline{v}_{\text{meas}}). \tag{11}$$

Advantageously, the matrix Left is constant and the inverse of the topology matrix  $\underline{P}_{\mathrm{D}}^{-1}$  must only be updated when the duty cycles change, i.e., for the required relatively slow phase current balancing in steady-state, the computational burden is moderate. As indicated in Fig. 4, PI controllers then ultimately regulate the deviations  $\Delta \underline{A}$  to zero.

# B. Small $D_{\rm DM}$ Approximation

For small (i.e., < 1%) values of  $D_{\rm DM}$ , which is, for example, the case in the considered HTS magnet application,<sup>3</sup> the computations in equation (9) can be simplified to minimize the computational effort by using

$$\sin(k\pi D^{+}) = \sin(k\pi D_{\rm CM})\cos(k\pi D_{\rm DM}) + \sin(k\pi D_{\rm DM})\cos(k\pi D_{\rm CM}) \approx \sin(k\pi D_{\rm CM})$$

(12)

and likewise for  $\sin(k\pi D^-)$ ,  $\sin((k+N)\pi D^+)$ , and  $\sin((k+N)\pi D^+)$  $N)\pi D^{-}$ ). This results in a simplified inverse for the topology matrix as

$$P_{D}^{-1}|_{\text{small D}_{DM}} = \left(\frac{(E)_{kk} | (F)_{kk}}{(G)_{kk} | (H)_{kk}}\right),$$

(13)

$^2 \text{This can be obtained by using the 4N-point DFT } \widetilde{\underline{\underline{s}}}_{4\text{N}}, \text{ or alternatively with a fast Fourier transformation (FFT). Note that } v_{\text{meas}} \text{ is proportional to}$ the dc-link capacitor dv/dt and hence the capacitor current; as finally only the current deviations are of interest, absolute values are not required.

$^3$ HTS magnet load with residual resistance in the order of  $1 \,\mu\Omega$ ,  $250 \,\mathrm{A}$ load current and  $1\,\mathrm{V}$  dc input voltage result in  $D_\mathrm{DM}\approx 0.0125\%.$

with  $k \in [0, N-1]$  and where

$$(E)_{kk} = \frac{-k\pi}{2(c-1)} \cdot \frac{e^{ik\left(\phi_{\text{inter}} - \frac{\pi}{N}\right)} + c}{\sin(k\pi D_{\text{CM}})}$$

$$(F)_{kk} = \frac{(k+N)\pi}{2(c-1)} \cdot \frac{e^{ik\left(\phi_{\text{inter}} - \frac{\pi}{N}\right)} + 1}{\sin((k+N)\pi D_{\text{CM}})}$$

$$(G)_{kk} = \frac{k\pi}{2(c-1)} \cdot \frac{e^{ik\left(\phi_{\text{inter}} - \frac{\pi}{N}\right)} - c}{\sin(k\pi D_{\text{CM}})}$$

$$(H)_{kk} = \frac{-(k+N)\pi}{2(c-1)} \cdot \frac{e^{ik\left(\phi_{\text{inter}} - \frac{\pi}{N}\right)} - 1}{\sin((k+N)\pi D_{\text{CM}})}$$

$$c = e^{-iN\phi_{\text{inter}}}.$$

(14)

Again, the first element (k = 0) of each diagonal matrix in the  $(2 \times 2)$  block-diagonal matrix must be calculated with L'Hôpital's rule. Compared with the general expression in (9), where six trigonometric function evaluations per entry of the block-diagonal matrix are needed, the approximation requires the computation of only a single sine function per entry, with a corresponding reduction of the computational burden.

# C. Robust Numerical Implementation

For the inverse of the topology matrix  $\underline{P}_{\mathrm{D}}$  to exist, the following two general conditions have to be met [10]:

- $\underline{X}$  is non-singular, and

- $Y V \cdot X^{-1} \cdot U$  is invertible.

This implies that a few discrete combinations of CM and DM duty cycles should be avoided, e.g., for N=2 this would be the combinations  $(D_{\rm CM}=\frac{3}{4},\ D_{\rm DM}=\frac{1}{4})$  and  $(D_{\rm CM}=\frac{2}{3},\ D_{\rm DM}=\frac{1}{3})$ ; the same applies to certain discrete branch duty cycle values  $D^+$  and  $D^{-}$ .

In case of the approximation for small DM duty cycles  $D_{\rm DM}$ , ensuring that both conditions above are satisfied and, thus, the entries of  $P_{\rm D}^{-1}\Big|_{\rm small\ D_{\rm DM}}$  are non-singular, i.e., the argument of the sine functions in the denominators does not equal an integer multiple of  $\pi$ , only the following CM duty cycles

$$D_{\rm CM} = \frac{1}{x} \quad \text{for } x \in \left[2, 2N\right],\tag{15}$$

must be avoided, e.g., for N=2 this would be the CM duty cycles  $D_{\rm CM}=\frac{1}{2},\frac{1}{3}$  and  $\frac{1}{4}.$  Choosing a CM duty cycle that

<sup>4</sup>Specifically, these are

$$\begin{split} &\left(D_{\mathrm{CM}} = \frac{\frac{1}{x} + \frac{1}{y}}{2}, \quad D_{\mathrm{DM}} = \frac{\frac{1}{x} - \frac{1}{y}}{2}\right), \text{ with} \\ &x \in \left[1, x_{\mathrm{max}} = \left\lfloor \frac{\sqrt{8N - 3} - 1}{2} \right\rfloor\right] \text{ and } y \in \left[x + 1, \left\lfloor \frac{2}{x}N - 1 \right\rfloor\right], \end{split}$$

$$\begin{split} D^{+/-}&=\frac{1}{3},\;\frac{2}{3}\;\text{and}\;1\qquad\qquad\text{for odd (non-prime)}\;N>3,\\ D^{+/-}&=\frac{1}{N}\cdot 2x\;\;\text{with}\;x\in\left[1,\frac{N}{2}\right]\qquad\text{for even}\;N, \end{split}$$

for even

$$N$$

that are divisible by 3, additionally:

$$D^{+/-}=\frac{3}{N}\cdot(2x+1) \ \text{ with } x\in\left[0,\frac{N}{6}-1\right].$$

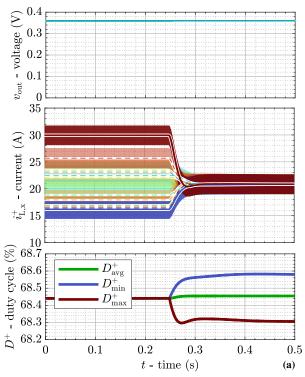

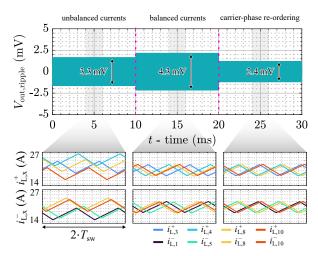

Fig. 5. Simulation results for a converter design with N=12 full-bridge phase modules,  $V_{\rm in}=1\,{\rm V}$ ,  $f_{\rm sw}=50\,{\rm kHz}$ , phase inductances  $L_{\rm x}^+=L_{\rm x}^-=1.2\,{\rm \mu H}$ , and up to  $\pm 50\%$  phase-to-phase mismatches of the transistors' on-state resistances for two operating points, i.e., (a)  $D_{\rm CM}=50\%$  and  $D_{\rm DM}=18\%$  and (b)  $D_{\rm CM}=53\%$  and  $D_{\rm DM}=0.0625\%$  which allows to employ the simplified computations for small DM duty cycles. The balancing controller is activated at  $t=0.25\,{\rm s}$  and adjusts the duty cycles of the individual phases  $D_{\rm x}^+$  and  $D_{\rm x}^-$  with  $x=1\dots N$  for the  $\bigoplus$ -branch and  $\bigoplus$ -branch respectively; only the minimum, maximum and average duty cycle of the  $\bigoplus$ -branch are shown for better visibility.

is close to these values is not problematic as long as a small margin of, e.g., 1% is kept.

In general, the CM duty cycle is a DoF in many applications and thus the "critical" CM, DM, or branch duty cycles can typically be avoided with minor adjustments of  $D_{\rm CM}$ . Furthermore, operation with many of the critical duty cycles is still possible, if the resulting singular entries of the topology matrix are avoided by replacing the respective rows (i.e., equations) with equations using higher-order harmonics. The choice of higher order harmonics is important such that the derived equations in (11) and (18) stay unchanged apart for the few block-diagonal entries in the (inverse) topology matrix. Specifically, a harmonic of order  $k_{\text{new}} = k + 2N$  should be used instead of a critical (i.e., singular) k-th entry in the original topology matrix, because the entries of the 2N-point DFT matrix  $\underline{\underline{S}}_{2N}$  repeat every 2N rows again, thus,  $\underline{\underline{S}}_{2N}$  would keep its unitary property and in this case even remains unchanged. Apart from modifying the entries of a few rows of the inverse topology matrix, only the corresponding rows of the truncated 4N-point DFT matrix  $\underline{\underline{S}}_{4N}$  must be replaced to extract the required new harmonics with order  $k_{\text{new}}$  from  $\underline{v}_{\text{meas}}$ .

# D. Simulation Results

The proposed phase current balancing method is verified by closed-loop simulation results of a full-bridge dc-dc step-down converter as shown in **Fig. 1b** but with N=12 full-bridge phase modules (i.e., 24 half-bridges in total). Large phase-to-phase mismatches of the transistor on-state resistances

$R_{

m ds(on)}$  of up to  $\pm 50\%$  have been introduced (with a random distribution), resulting in a wide variation of the average phase currents before the controller is activated at  $t=0.25\,{\rm s}$  in Fig. 5ab. Whereas in Fig. 5a,  $D_{\rm CM}=50\%$  and  $D_{\rm DM}=18\%$  require the full computations with (9), Fig. 5b considers  $D_{\rm CM}=53\%$  and  $D_{\rm DM}=0.0625\%$  (e.g., assuming a  $5\,{\rm \mu}\Omega$  parasitic resistance of an HTS magnet load) and thus the small  $D_{\rm DM}$  approximation (with lower computational effort) from (13) is employed. In both cases, the proposed balancing method achieves almost perfect current sharing among the phases. However, the output voltage quality could be adversely affected by the then (necessarily) unequal duty cycles of the half-bridges, as is evident from the increase of the output voltage ripple observed in Fig. 5b (Section IV-D discusses carrier-phase reordering as a countermeasure).

## IV. IMPLEMENTATION AND IMPROVEMENT VECTORS

In the following, a few important aspects regarding the implementation of the sensing circuitry, and two possibilities for improving the overall system performance are briefly discussed.

## A. Input-Side Decoupling Impedance

Considering the power circuit from **Fig. 1b**, it is important to note that most of the pulsed switching ripple current from the  $\oplus$ - and  $\ominus$ -branches should close through the bulk dc-link capacitor, whose  $\mathrm{d}v/\mathrm{d}t$  is sensed and used for estimating the phase current unbalance. This requires that any upstream converter unit that provides the dc input voltage has either

Fig. 6. Indirect input capacitor current sensing circuit for distributed (e.g., amongst full-bridge phase modules) dc-link capacitors.

sufficient output impedance or the interconnection impedance is sufficiently large. A rule of thumb can be provided based on a worst-case allowable ripple current share of  $x_{\rm L,in}\approx 5\dots 10\%$  not flowing through the dc-link capacitor. Then, assuming zero output impedance of the upstream converter, a decoupling inductance of

$L_{\mathrm{input}} \ge \frac{1}{\omega^2} \cdot \frac{1}{C_{\mathrm{in}}} \cdot \frac{1 - x_{\mathrm{L,in}}}{x_{\mathrm{L,in}}}$  (16)

at the first switching harmonic with  $\omega = 2\pi \cdot f_{\mathrm{sw}}$  is required.

## B. Sensing Circuit for Distributed DC-Link Capacitors

The circuit that is used for indirectly sensing the input capacitor current waveform is depicted in Fig. 6. In contrast to the simplified variant from Fig. 1, the case of a distributed dc-link capacitor bank, as often found in phase-modular designs of multi-phase converters, is considered. The individual dc-link capacitor dv/dt are measured using dedicated  $R_1C_1$  branches summed up at a fully-differential amplifier, which is configured as an active high-pass filter with  $R_1$  and  $C_f$  utilized as highfrequency roll-off components;  $R_2$  and  $C_2$  form an anti-aliasing filter at the input of the differential analog-to-digital converter (ADC). Reconstructing the required 2N harmonics below  $f_{\rm eff}$ used for the phase current estimation requires a measurement bandwidth of at least BW =  $2 \cdot 2N f_{sw}$ . For a converter design with N=12 and  $f_{\rm sw}=10\,{\rm kHz}$  this would be a bandwidth of  $\mathrm{BW} = 480\,\mathrm{kHz}$ . In case higher-order harmonics are required to operate with "critical" duty cycle combinations as discussed in **Section III-C**, up to twice that bandwidth would be needed.

In practice, there are parasitic elements  $L_{\rm par}$  and  $R_{\rm par}$  due to the interconnections of the distributed dc-link capacitors, as indicated in **Fig. 6**. These parasitics, if the dc-link capacitor banks are not carefully designed, might lead to oscillations between the dc-link capacitors of the different phases. This will adversely impact the current balancing control, as parasitic circulating currents are not considered in the derivation of the Fourier series in equation (5). For the considered system with N=12 full-bridge phase modules, simulations indicate that parasitics in the order of  $L_{\rm par}\approx 10\,{\rm nH}$  and  $R_{\rm par}\approx 200\,{\rm \mu\Omega}$  (randomly distributed among the phase modules) do not impact the current balancing performance noticeably.

#### C. Phase Inductance Mismatch Estimation

The proposed phase current balancing method from Section III-A assumes equal phase inductances  $L_{\rm i}^+=L_{\rm i}^-$  for all phases in the derivation of the expressions for the current imbalance information  $\Delta\underline{A}$ . Whereas small inductance variations in the order of  $\pm 10\%$  do not noticeably impair the performance of the corresponding balancing controller implementation based on equation (11), larger variations of up to, e.g.,  $\pm 30\%$  must be expected in certain applications. Then, to still achieve appropriate phase current balancing performance, the effect of phase inductance mismatches on equation (5) should be taken into account.

The inductance variations are in general unknown and an a priori measurement (or calibration) is often not feasible because of costs and possibly changing conditions during the lifetime due to aging effects. However, whereas the ac components of the dc-link capacitor current are mostly defined by the average phase current and the switching states of the bridge-legs, the ac components of the output capacitor result only from the ac (ripple) components of the phase currents, i.e., change with the individual inductance values. Advantageously, therefore, a similar approach as for estimating the phase current imbalance (see Section III-A) can be used to estimate the relative inductance variations during converter operation by means of a single (indirect, again via the dv/dt) measurement of the *output* capacitor current with a sensing circuit like in Fig. 6.5 Again, the harmonic spectrum is utilized to estimate the phase inductance variations: The vector  $\tilde{\underline{L}} = [\frac{1}{L_1^+}, \ \frac{1}{L_1^-}, \ \frac{1}{L_1^+}, \ \frac{1}{L_1^-}, \ \dots]^T$  containing the phase inductance mismatch information can be determined by considering the complex-valued Fourier coefficients for the output capacitor current waveform and applying similar transformations as in equation (6), i.e.,

$$\begin{split} \widetilde{\underline{L}} &= \underline{\underline{S}}_{2N}^{-1} \cdot \underline{\underline{P}}_{L}^{-1} \cdot \underline{\underline{c}}_{meas, V_{out}} \\ &= \underline{\underline{S}}_{2N}^{-1} \cdot \underline{\underline{P}}_{L}^{-1} \cdot (\underline{\widetilde{\underline{S}}}_{4N} \cdot \underline{\underline{v}}_{meas, V_{out}}), \end{split} \tag{17}$$

where  $P_{\rm L}$  is again a  $(2\times 2)$  block-diagonal matrix and  $S_{\rm 2N}$  is the 2N-point DFT matrix; note the similarity to (8). This information can subsequently be used to compute a refined phase current unbalance estimate by including the effect of inductance variations as  $\Delta A = \Delta A_{\rm iCin} + \Delta A_{\rm L}$  in (11):

$$\Delta \underline{A} = \underline{\underline{\text{Left}}} \cdot \underline{P}_{D}^{-1} \cdot (\widetilde{\underline{S}}_{4N} \cdot \underline{v}_{\text{meas}} - C_{\underline{L}} \cdot \underline{S}_{2N} \cdot \widetilde{\underline{L}}). \quad (18)$$

There,  $\underline{C}_{\rm L}$  represents a  $(2\times 2)$  block-diagonal matrix that is used to obtain the correction terms  $\Delta \underline{A}_{\rm L}$ . A more detailed description is beyond the scope of this paper and will be addressed in future work.

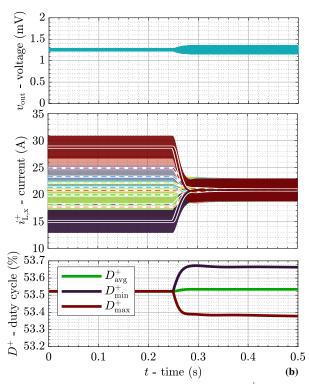

### D. Carrier-to-Phase Re-Ordering

As observed in **Fig. 5b**, the output voltage exhibits an increased ripple after the balancing controller becomes active, because of

<sup>&</sup>lt;sup>5</sup>Note that the output capacitor is typically smaller in size compared to the dc-link capacitor, and can be centrally placed in contrast to the practically required distributed placement of the input dc-link capacitor bank to keep the commutation loops as small as possible.

the according minor modifications of the individual bridge-leg duty cycles. One approach to mitigate this increased ripple consists in modifying the intra-branch interleaving angles  $\phi_{\mathrm{intra}}$ as in [11], [12]. For example, in [12], the case of non-ideal ripple cancellation due to inductance tolerances is considered and a suitable rearranging of the carrier-to-phase assignment is proposed such that phases with similar peak-to-peak ripple amplitudes operate with 180° phase shift; this reduces the measured voltage ripple by up to 45%. However, the approach is limited to the effect of inductance variations only, requires a current sensor, and a dedicated calibration switching sequence to determine an improved carrier-to-phase assignment.

In the case at hand, an increased output voltage ripple can as well arise from phase inductance tolerances, but in particular also due to the adjustment of the individual bridge-leg duty cycles by the proposed current balancing controller. Here, an improved carrier-to-phase assignment at either the intra-branch or even the inter-branch<sup>6</sup> level resulting in better ripple cancellation can be found based on the current balancing controller outputs  $\Delta D^+$  and  $\Delta D^-$  from Fig. 4 and, possibly, also based on the phase inductance estimation (see Section IV-C). Advantageously, no further sensors or additional calibration procedures are needed. In the most fundamental case of only using the current balancing controller outputs  $\Delta D^+$  and  $\Delta D^-$  and restricting the re-ordering to only the intra-branch level by simply assigning the carriers according to the duty cycle values, already a reduction of the output voltage ripple by around 44% is achieved, see Fig. 7.

### V. CONCLUSION

In certain applications of multi-phase full-bridge dc-dc converters, losses (e.g., for operation inside of cryostats when supplying HTS magnets as considered here) and/or costs prevent the use of per-phase current sensors that are otherwise employed to ensure balanced phase currents. Therefore, this paper introduces a new phase current balancing control method based on indirectly sensing the dc input capacitor current via the dv/dt and using the known switching states of the converter phases. Detailed mathematical derivations lead to a computationally efficient frequency-domain processing method. Further, for very small output voltages (as, e.g., for the considered application with HTS magnet loads) the computations can be simplified. Both cases are verified by detailed circuit simulations of a system with 12 full-bridge phase modules. Practical aspects such as the realization of the dc input capacitor sensing circuitry for cases with the dc-link capacitor distributed among the phase modules are discussed. Finally, the current balancing control can be improved by means of an additional phase inductance mismatch estimation based on indirectly sensing the output capacitor current, and the output voltage ripple can be decreased by employing a loweffort carrier-to-phase re-assignment based on the balancing

<sup>6</sup>The intra-branch level implementation does not consider the mutual cancellation of the output current ripples from the two branches, whereas this superposition would be included in an inter-branch level consideration.

Fig. 7. Carrier-to-phase re-ordering on the intra-branch level utilizing the duty cycle adjustments from the current balancing controller. The simulation results show the output voltage ripple (ac coupling) at the top and zoomed views of four (out of N=12) exemplary phase currents of the (+)- and the (-)-branch.

controller outputs; these aspects will be analyzed in more detail in the scope of future work.

#### ACKNOWLEDGMENT

This work was performed under the auspices and with support from the Swiss Accelerator Research and Technology (CHART) program (www.chart.ch).

#### REFERENCES

- [1] CERN, "Future circular collider study: Exploring concepts and technologies for the next generation of powerful particle colliders, accessed 2022-11-10. [Online]. Available: https://fcc.web.cern.ch/

- [2] D. Cao, D. Zhang, J. W. Kolar, and J. Huber, "Conceptualization of a cryogenic 250-A power supply for high-temperature-superconducting (HTS) magnets of future particle accelerators," in *Proc. 11th Int. Conf.* Power Electron. (ICPE-ECCE Asia), Jeju, South Korea, May 2023, pp. 688-696.

- Parisi, "Multiphase buck design from start to finish (Part 1)," 2021, Application Report. [Online]. Available: https://www.ti.com/lit/an/ slva882b/slva882b.pdf

- [4] O. Garcia, P. Zumel, A. de Castro, P. Alou, and J. A. Cobos, "Current selfbalance mechanism in multiphase buck converter," IEEE Trans. Power Electron., vol. 24, no. 6, pp. 1600–1606, 2009. [5] D. Costinett, D. Seltzer, D. Maksimovic, and R. Zane, "Inherent volt-

- second balancing of magnetic devices in zero-voltage switched power converters," in Proc. IEEE Appl. Power Electron. Conf. (APEC), Long Beach, CA, USA, Mar. 2013, pp. 9-15.

- [6] S. Mariethoz, A. Beccuti, and M. Morari, "Model predictive control of multiphase interleaved DC-DC converters with sensorless current

- limitation and power balance," in *Proc. IEEE Power Electron. Spec. Conf. (PESC)*, Rhodes, Greece, Aug. 2008, pp. 1069–1074.

[7] Y. Cho, A. Koran, H. Miwa, B. York, and J.-S. Lai, "An active current reconstruction and balancing strategy with dc-link current sensing for a multi-phase coupled-inductor converter," IEEE Trans. Power Electron., vol. 27, no. 4, pp. 1697-1705, 2012.

- [8] A. Bogdanovs, O. Krievs, and J. Pforr, "Indirect dc link current measurement technique using an op-amp circuit in an automotive dc converter with coupled inductors," in *Proc. Power Convers. Intelligent*

- Motion Conf. (PCIM Europe), Nuremberg, Germany, Jul. 2020. G. Eirea and S. R. Sanders, "Phase current unbalance estimation in [9] G. Eirea and S. R. Sanders, "Phase current unbalance estimation in multiphase buck converters," *IEEE Trans. Power Electron.*, vol. 23, no. 1, p. 137–143, 2008.

- M. Saadetoglu and S. M. Dinsev, "Inverses and determinants of  $n \times n$

- block matrices," *Mathematics*, vol. 11, no. 17, 2023.

[11] S. Waffler, J. Biela, and J. Kolar, "Output ripple reduction of an automotive multi-phase bi-directional dc-dc converter," in *Proc. IEEE* Energy Convers. Congr. Expo. (ECCE USA), San Jose, CA, USA, 2009, p. 2184–2190.

- [12] O. Garcia, A. de Castro, P. Zumelis, and J. A. Cobos, "Digital-controlbased solution to the effect of nonidealities of the inductors in multiphase converters," IEEE Trans. Power Electron., vol. 22, no. 6, pp. 2155-2163,